# Design of application-specific amplifiers with OpAmps

# Structured design approach

- Benefits

- First time right

- Predictable results

- Manageble design process

- Guaranteed by design

- Knowledge building

- Features

**HEADER2**

- Clear distinction between concepts and implementation

- SLiCAP: Python based integrated design and HTML documentation tool

- Use dedicated models for specific performance aspects during various stages of the design

- Practical approach:

- 1. Specification of performance, environment and costs

- 2. Concept development

- 3. Implementation study (technology and components)

- 4. Circuit engineering

- 5. Design verification (simulation, prototype, ... )

- 6. Design documentation (design, production, test, ...)

- Clear theoretical basis:

- Physics

- Signal processing

- Control theory

- Network theory

Data Sheet

Slew rate: 870 V/µs 0.1% settling time: 9 ns

APPLICATIONS

Filters ADC drivers Output buffe

High speed

–3 dB bandwidth (G = 1,  $R_L$  = 100 Ω): 1050 MHz

Common-mode capacitance: 1.3 pF typical

Low distortion: -90 dBc at 10 MHz (G = 1, R<sub>L</sub> = 1 k $\Omega$ )

Supply quiescent current per amplifier: 19 mA typical

Voltage noise: 4 nV/√Hz at 100 kHz Current noise: 2.5 fA/√Hz at 100 kHz

**FEATURES**

- Systems engineering

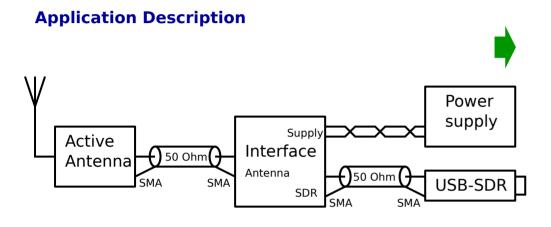

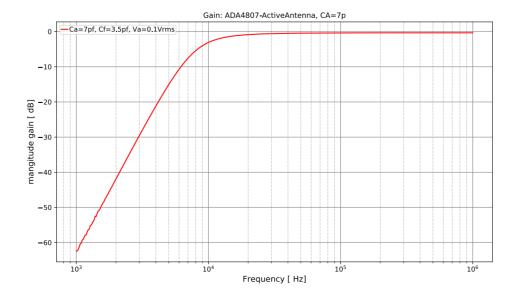

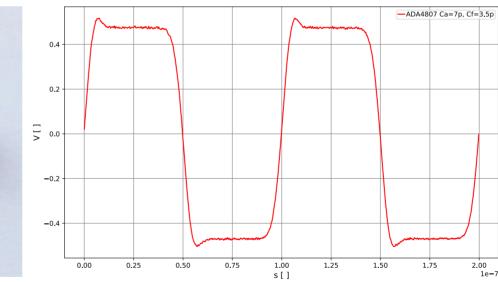

## **Application data:**

- Antenna length: 0.5m

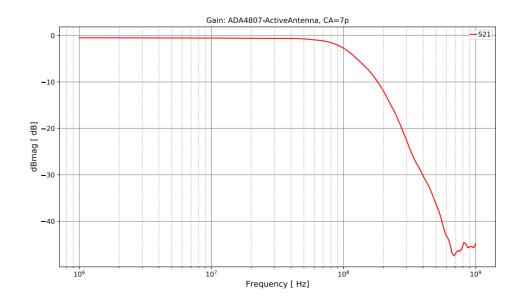

- Frequency range: 10kHz 30MHz

- E-field at antenna: 0.45V<sub>rms</sub>/m

- Output signal: 0dBm @ 500hm

- Power supply voltage: 7V

- Power dissipation < 250mW

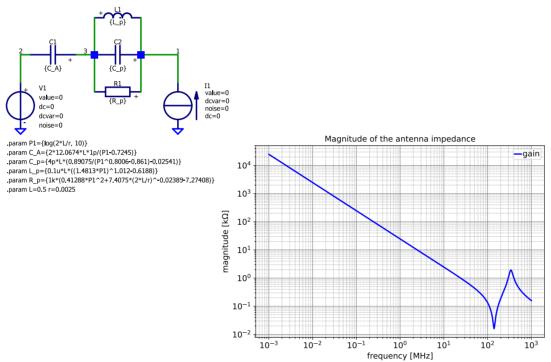

## **Source modeling**

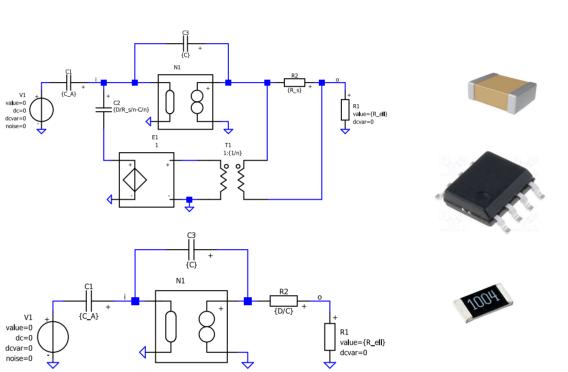

### **Concept development** Implementation study

Low Noise, 1 GHz FastFET Op Amps

# ADA4817-1/ADA4817-2

## CONNECTION DIAGRAMS

Figure 1. 8-Lead LFCSP (CP-8-13) ADA4817-1 TOP VIEW (Not to Scale)

Figure 2. 8-Lead SOIC (RD-8-1) 16 FB1 15 PD1 14 +V<sub>S1</sub> 13 OUT1

Figure 3, 16-Lead LFCSP (CP-16-20)

DEVICE MARKING INFORMATION

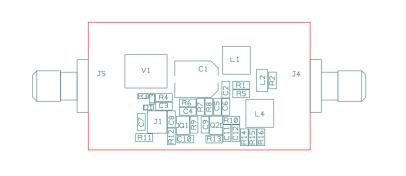

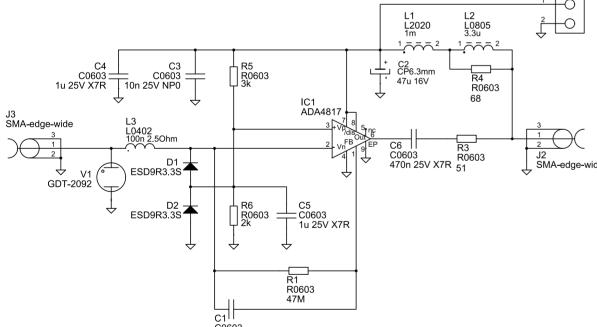

# Schematic design

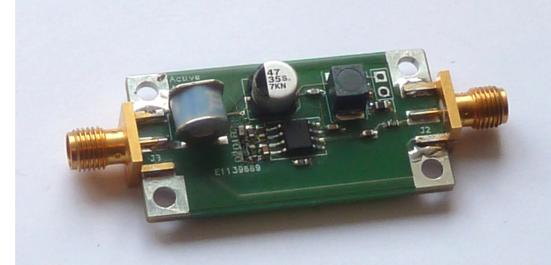

**PCB** design

## **Assemby and test**

## ESD9R3.3S, SZESD9R3.3S

## **ESD Protection Diode**

# **Ultra-Low Capacitance**

The ESD9R is designed to provide ESD protection for ASSPs and ASICs used in ultra low current applications such as human body sensors. These devices have been designed for leakage under 1 nA from 0°C to 50°C when turned off. During an ESD event, these devices turn on to clamp the ESD to a safe voltage level for the IC. These devices have the added benefits of low capacitance for high speed data lines and small package size for space constrained designs.

# Specification Features: Ultra-Low Leakage < 1 nA Ultra-Low Capacitance 0.5 pF

- · Low Clamping Voltage

- Low Clamping Voltage

Small Body Outline Dimensions:

0.039" x 0.024" (1.00 mm x 0.60 mm)

Low Body Height: 0.016" (0.4 mm)

Stand-off Voltage: 3.3 V

Response Time < 1.0 ns

IECO1000-4-2 Level 4 ESD Protection

SZ Prefix for Automotive and Other Applications Requiring Uniq Site and Control Change Requirements; AEC-Q101 Qualified and PADA Carable.

- This is a Pb-Free and Halogen-Free Devi

| MAXIMUM RATINGS                                                        |               |                  |            |

|------------------------------------------------------------------------|---------------|------------------|------------|

| Rating                                                                 |               | Symbol           | Value      |

| IEC 61000-4-2 (ESD) Co                                                 | ontact<br>Air |                  | ±10<br>±15 |

| НВМ                                                                    |               |                  | ±16        |

| Total Power Dissipation on FR-5 Bo<br>(Note 1) @ T <sub>A</sub> = 25°C | oard          | PD               | 150        |

| Storage Temperature Range                                              |               | T <sub>stg</sub> | -55 to +15 |

| Junction Temperature Range                                             |               | TJ               | -55 to +1  |

| Lead Solder Temperature - Maximu                                       | ım            | TL               | 260        |